2014年5月12日至13日,由华芯承担的国家核高基重大专项“嵌入式存储器IP核开发及应用”课题验收会在西安隆重召开。

验收会现场

验收会现场

会议由核高基重大专项实施管理办公室张景波处长主持,浙江大学集成电路与基础软件研究院严晓浪院长担任专家组组长,总共15位技术和财务专家组成专家组。课题责任专家李云岗、核高基实施管理办公室衣丰涛处长、陕西省工信厅高翔处长和西安市工业和信息化委员会薛铁英处长等领导出席本次验收会议。华芯总裁兼CEO、西安华芯董事长高传贵,华芯高级副总裁、西安华芯总经理、课题负责人任奇伟以及联合单位负责人及课题管理办公室相关人员参加验收会议。

测试检查组专家听取了课题完成情况报告、第三方测试评价报告、应用报告,审查了课题组提交的资料文档,查看了测试演示和产品成果展示。任务验收组和财务验收组分别对任务和财务执行情况进行了严格审查,经过专家组询问、讨论,一致同意课题通过验收。专家组充分肯定了华芯近年来的发展,对华芯在存储器领域的技术创新给予高度评价,对课题良好的管理组织工作也给予了高度肯定。至此经过历时两年半时间的不懈努力,课题任务圆满完成。

嵌入式存储器SRAM IP核是数字逻辑集成电路的核心模块之一,有着巨大的市场需求。本课题采用中芯国际65nm、55nm和40nm低漏电逻辑工艺研发了单口同步SRAM IP核。研发的SRAM编译器支持位宽2~64bit,深度512~512K字,具有内建自测试、自修复、冗余技术、功耗控制、数字水印等可配置功能,可生成SRAM IP相关的仿真模型、版图和设计文档,具有图形化界面,支持Windows、Unix和Linux等多种运行平台和主流EDA环境,并完成了在SoC芯片中的应用验证。经过第三方评测,本课题完成了任务合同书规定的研究内容,技术成果达到了规定的考核指标。

课题执行期间,课题组完成了SRAM IP核的低功耗、高密度、高可靠单元以及内建自测试、自修复等关键技术研究,申请了发明专利21项(其中: 国际发明专利2项, 国内发明专利19项),发表了论文14篇,并建立了一支从事SRAM IP核技术创新、产品研发和支持服务团队。

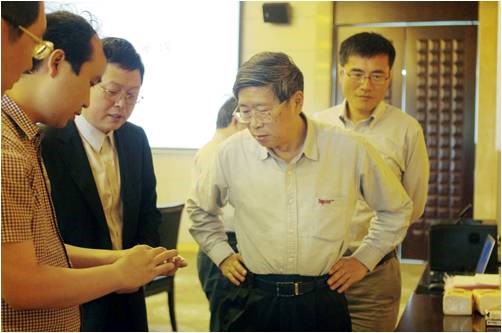

专家组现场查验课题成果

专家组现场查验课题成果

专家组现场查验课题成果

华芯致力于为客户提供完整的存储系统解决方案,包括嵌入式静态随机存储器SRAM, DDR PHY/MC 及片外DRAM芯片完整的存储系统优化设计及支持。通过本课题的实施,目前华芯已经能够为客户提供基于中芯国际65nm、55nm和40nm三代工艺的SRAM IP核及其编译器,并能够根据客户的需求开展SRAM IP核的定制化设计服务。